Last Updated on August 9, 2023 by Mayank Dham

In computer architecture, where innovation propels technological progress, the emergence of RISC-V has sparked a revolution. RISC-V, an open-source instruction set architecture (ISA), stands as a beacon of flexibility, modularity, and accessibility, reshaping the landscape of processor design and fueling the aspirations of a diverse range of industries. This article delves into the world of RISC-V, exploring its origins, principles, benefits, and potential to shape the future of computing.

A Glimpse into RISC-V’s Origins

RISC-V, pronounced "RISC Five," traces its roots back to the University of California, Berkeley, where it was born in 2010. A team led by Professor Krste Asanović embarked on a journey to design an open-source instruction set architecture that would break free from the constraints of proprietary designs, enabling a new era of innovation and collaboration. The project’s name, "RISC-V," signifies its heritage as a "RISC" (Reduced Instruction Set Computer) architecture, while "V" represents the fifth major version of the team’s endeavor.

Foundations of RISC-V

At its core, RISC-V embodies simplicity and modularity. Unlike proprietary ISAs that are closely guarded and often require licensing fees, RISC-V is open and freely accessible. Its modular design allows developers to choose and implement only the instructions that are relevant to their specific application, minimizing unnecessary complexity. This modularity not only enhances efficiency but also empowers customization, making RISC-V adaptable to a wide array of use cases.

Key Features and Benefits of RISC-V

1. Openness and Accessibility: RISC-V’s open-source nature encourages collaboration and innovation across academia, research, and industry. It democratizes access to processor design, enabling startups, researchers, and hobbyists to experiment and create without barriers.

2. Modularity and Flexibility: RISC-V’s modular architecture lets designers create processors tailored to specific workloads. This adaptability is particularly advantageous in embedded systems, Internet of Things (IoT) devices, and edge computing scenarios.

3. Scalability: RISC-V offers scalability from microcontrollers to high-performance server processors. This scalability makes it a compelling choice for a diverse range of applications, from low-power wearables to supercomputers.

4. Reduced Design Complexity: By emphasizing a streamlined instruction set, RISC-V simplifies processor design and verification, potentially leading to quicker development cycles and reduced manufacturing costs.

5. Innovation and Research: RISC-V’s open nature fosters a fertile ground for research and experimentation in computer architecture, enabling novel ideas to be explored without the constraints of proprietary licenses.

6. Ecosystem Growth: The RISC-V ecosystem is rapidly expanding, with various companies, including established players and startups, developing RISC-V-based products, tools, and services.

Understanding the RISC-V Architecture

RISC-V (pronounced "RISC Five") is a free and open source instruction set architecture (ISA) that is designed to be simple, modular, and extensible. Unlike proprietary ISAs, RISC-V is not tied to a specific company or vendor, which makes it highly versatile and adaptable to a wide range of applications. Its architecture is built upon a few key principles:

1. Reduced Instruction Set: RISC-V adheres to the philosophy of a reduced instruction set architecture, or RISC. This means that its instruction set is deliberately kept minimal, focusing on a small set of simple instructions that can be executed quickly. The simplicity of instructions facilitates faster execution and easier design.

2. Modularity: One of the standout features of RISC-V is its modular design. The architecture provides a base set of instructions, and additional optional instruction extensions can be added as needed for specific applications. This modularity allows system designers to tailor the instruction set to match the requirements of their target applications.

3. 32-Bit and 64-Bit Variants: RISC-V offers both 32-bit and 64-bit variants, providing flexibility in addressing different computing needs. The 32-bit version is suitable for low-power embedded systems and microcontrollers, while the 64-bit version caters to higher performance computing environments.

4. Load-Store Architecture: RISC-V follows a load-store architecture, which means that arithmetic and logic operations are performed only on data loaded from memory and then stored back. This approach simplifies the instruction set and enhances the efficiency of memory operations.

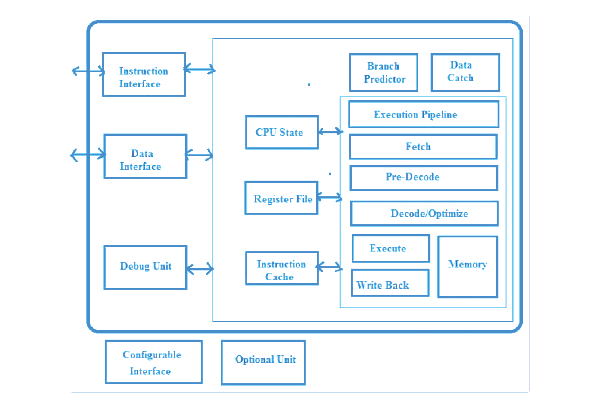

Working of RISC-V

The operation of a RISC-V processor can be broken down into several stages:

1. Instruction Fetch (IF): The processor fetches the instruction from memory using the program counter (PC) as a reference. The PC is incremented to point to the next instruction.

2. Instruction Decode (ID): In this stage, the fetched instruction is decoded to determine the operation to be performed and the operands involved.

3. Execution (EX): The actual computation or operation specified by the instruction is carried out. This could involve arithmetic, logic, or other operations.

4. Memory Access (MEM): If the instruction involves memory access (e.g., load/store operations), this stage is responsible for reading from or writing to memory.

5. Write Back (WB): The result of the execution is written back to the register file if necessary. This stage ensures that the updated data is available for subsequent instructions.

Challenges and Future Prospects of RISC-V

Despite its promise, RISC-V faces challenges in achieving widespread adoption and compatibility across diverse hardware and software ecosystems. The ISA’s relative newness also means that developers may encounter limitations in terms of available tools, libraries, and documentation compared to more established architectures.

However, RISC-V’s trajectory remains undeniably upward. As the ecosystem matures, these challenges are likely to diminish, opening the door to a future where RISC-V plays a pivotal role in shaping computing landscapes and empowering new frontiers of technological advancement.

Conclusion

RISC-V has emerged as a transformative force in the world of computer architecture, embodying principles of openness, modularity, and flexibility. With its potential to drive innovation, democratize processor design, and revolutionize various industries, RISC-V stands as a testament to the power of collaborative, open-source endeavors in shaping the future of computing. As RISC-V continues to gather momentum, its impact is poised to reach new heights, leaving an indelible mark on the ever-evolving landscape of technology.

Frequently Asked Questions (FAQs)

Here are some of the frequently asked questions on risc-v architecture.

1: What is the RISC-V architecture, and how is it different from other processor architectures?

Answer: RISC-V architecture is an open source instruction set architecture (ISA) designed for processors. It is distinct from other architectures in that it is modular and extensible, allowing users to tailor the instruction set to their specific requirements. RISC-V, unlike proprietary ISAs, is not owned by a single company, making it open and accessible to all for development and innovation.

2: How does RISC-V achieve modularity in its design?

Answer: RISC-V achieves modularity through its base instruction set and optional instruction extensions. The base set provides essential instructions, while extensions add specific functionalities. Developers can choose and implement only the necessary extensions, tailoring the processor to the requirements of their applications. This modularity promotes efficiency and flexibility in design.

3: What are the advantages of RISC-V’s load-store architecture?

Answer: RISC-V’s load-store architecture simplifies instruction execution by performing arithmetic and logic operations exclusively on data loaded from memory. This approach minimizes the complexity of instructions, reduces memory access times, and enables efficient pipelining. It also allows for better memory hierarchy management and optimization.

4: How does RISC-V handle both 32-bit and 64-bit variants?

Answer: RISC-V supports both 32-bit and 64-bit variants to cater to diverse computing needs. The 32-bit version is suitable for embedded systems and applications where power efficiency is crucial. The 64-bit version caters to more demanding computing tasks, such as high-performance computing, where larger memory addressing and higher precision arithmetic are required.

5: How does the open source nature of RISC-V architecture benefit developers and industries?

Answer: The open source nature of RISC-V empowers developers and industries in multiple ways. It enables customization of processor designs, encouraging innovation and specialization for specific applications. Developers can access the architecture’s specifications, collaborate, and share knowledge, leading to faster development cycles and improved solutions. The open ecosystem also reduces licensing costs and dependencies on single vendors, fostering healthy competition and a vibrant community-driven development landscape.